# 2014~2015 学年

# 数字逻辑设计实践教学计划

### 1、 基本情况:

1、总学时: 32学时

2、学时比例: 1(课内): 1.5(课外)

3、学 分: 1学分

4、适用范围: 2013级4、6、8、11、16、22系学生

5、先修课程: 高等数学、物理、数字逻辑电路

6、时间: 2014.10~2015.1

7、实验教材: 《数字逻辑设计实践》徐莹隽、常春等编著,高等教育出版社

#### 2、 教学要求:

#### 预习要求:

- 1、进实验室前**必须**完成本次实验预习报告,内容包括

- a) 实验电路功能描述、系统框图和详细设计过程

- b) 实验电路原理图

- c) 实验电路硬件连接图

- d) 如果实验有预习思考题,提交预习思考题答案

- 2、预习报告写在实验报告的实验原理部分,如没有把握,也可先写在其他纸上,实验完成后重誊写到实验报告上

- 3、实验电路必须在进实验室前完成搭接,实验室内以电路调试为主

- 4、电工电子实验中心的网站地址为: <a href="http://eae.seu.edu.cn">http://eae.seu.edu.cn</a>, 预习时请访问该平台以了解您准备完成的实验内容是否有变动、提示或其他通知。

#### 实验要求:

- 1、实验采用集中授课+开放实验模式,第一次实验时请仔细阅读开放实验规章制度,并在 以后的实验中认真遵守

- 2、每次实验要带校园卡、元器件、单股连接线、丁字线和所发的面包板。丁字线和面包板请妥善保管,勿丢失或损坏,否则将照价赔偿

- 3、在进入实验室时,请在刷卡机上出示您的校园卡,在刷卡机分配的实验室和实验座位上完成实验,严禁串座

- 4、实验前先检查自己座位上的仪器、如有缺失或损坏请及时通知指导老师处理。实验过程中如果发生仪器故障,也请和值班教师联系,值班教师检查确认后用备用仪器更换,严禁自己用其他实验座位上的仪器更换

- 5、按实验设计方案搭接和测试电路,认真检查确保无误后方可通电测试

- 6、认真记录实验数据和实验波形,所有数据和波形都要分析判断,确认正确

- 7、要求实物验收的实验内容,完成并记录所有实验数据后,提请指导老师验收,验收通过后方可拆除电路结束实验

- 8、实验过程中遇到故障要独立思考,耐心查找故障原因并排除,记录故障现象、排除故障的过程和方法

- 9、实验中若发生异常现象,应立即切断电源,并通知指导老师处理。如有元器件损坏,可到仪表室购买

- 10、 开放实验每次至少要完成一项实验内容,单次实验时间不少于1个小时

- 11、 实验中途请勿随意离开实验室,如确实有特殊情况请向指导教师请假

- 12、 实验完成后请将仪器归位并关闭仪器电源、整理线缆、打扫干净实验桌面,然后刷卡下机

#### 实验报告要求:

- 1. 实验报告应该包括以下几个部分

- > 实验目的和要求

- 实验原理,包括实验电路的设计过程、系统框图、原理图、硬件连接图、测试方案等,要求在实验前完成

- > 实验仪器,实验中用到的仪器设备

- ➤ 实验记录,记录实验具体步骤、原始数据、实验过程、实验中遇到的故障现象、 排除故障的过程和方法等

- > 实验分析,对实验结果进行分析比对

- 实验小结,总结实验完成情况,对设计方案和实验结果做必要的讨论,简述实验 收获和体会

- > 实验思考题,如有,提交思考题答案

- > 参考资料,记录实验过程阅读的有关资料,包含资料名称、作者等

- 2. 数字电路实验结果验证一般包括真值表验证、波形验证、功能验证

- ▶ 真值表验证结果,要求用表格记录

- ▶ 波形验证结果,要求记录在坐标纸上,记录的时候注意多路波形之间的时序关系

- ▶ 功能验证结果,要求用表格记录

- 3. 实验报告必须在指定时间完成并提交

## 3、 实验教学计划

| 周次 | 内容           | 实验模式 | 学时 | 教材                       |

|----|--------------|------|----|--------------------------|

| 06 |              | 集中授课 | 3  | <b>英10</b> 0英            |

| 07 | 组合逻辑电路       | 开放实验 | 3  | 第1、2、3章                  |

| 08 |              | 集中授课 | 3  |                          |

| 09 | FPGA 组合逻辑设计  | 开放实验 | 3  | 第3、7章                    |

| 10 | 时序逻辑电路       | 集中授课 | 3  | 第4章                      |

| 11 | 7777         | 集中验收 | 3  | 71, 1                    |

| 12 |              | 开放实验 | 3  |                          |

| 13 | FPGA 时序逻辑设计  | 集中验收 | 4  | 第 4、7 章                  |

| 14 | EDCA 石(水)八)。 | 开放实验 | 3  | <b>数</b> ( 7 <del></del> |

| 15 | FPGA 系统设计    | 集中验收 | 4  | 第6、7章                    |

| 16 | 期末考试         | 集中上课 | 3  |                          |

## 4、 评分和考核方法

实验过程采用积分考核方式,总积分为 300, 实验总评采用等级制,等级和积分对应关系为: 优(250 – 300), 良(225 – 250), 中(200 – 225), 及格(165 – 200), 不及格(0 – 165)。 具体积分分布如下表所示

| 实验名称             | 预习报告 | 预搭接 | 实验验收 | 实验报告 |  |

|------------------|------|-----|------|------|--|

| 组合逻辑电路           | 5    | 5   | 10   | 10   |  |

| FPGA 组合逻辑设计      | 5    | 5   | 10   | 10   |  |

| 时序逻辑电路(第10周实验)   | 5    | 5   | 5    | 1.0  |  |

| 时序逻辑电路(第11周实验)   | 5    | 5   | 15   | 10   |  |

| FPGA 时序逻辑设计      | 10   | 0   | 20   | 10   |  |

| FPGA 系统设计        | 10   | 0   | 40   | 10   |  |

| 期末考试             | 75   |     |      |      |  |

| 其他(实验态度、考勤、违纪违规) |      |     | 15   |      |  |

## 5、 本学期开放时间安排

1、集中上课周次(第6、8、10、11、13、15 周)

▶ 周一~周四

17:30 ~ 21:00

▶ 周六

09:30 ~ 16:30

▶ 其他时间如实验室有空位也可插班实验

2、开放实验周次(第7、9、12、14 周)

▶周一

14:00 ~ 21:00

▶ 周二~周四

09:30 ~ 21:00

▶ 周五

09:30 ~ 17:00

▶ 周六

09:30 ~ 16:30

- 3、法定假期和校历规定的假期,实验室不开放

- 4、开放时间临时变更,将在实验中心主页上提前通知,来实验室前最好访问实验中心主页确 认是否开放

## 实验一、组合逻辑电路

## 1、 学习目标:

- ① 认识数字集成电路,能识别各种类型的数字器件和封装

- ② 掌握小规模组合逻辑和逻辑函数的工程设计方法

- ③ 掌握常用中规模组合逻辑器件的功能和使用方法

- ④ 学习查找器件资料,通过器件手册了解器件。

- ⑤ 了解面包板的基本结构、掌握面包板连接电路的基本方法和要求

- ⑥ 了解实验箱的基本结构,掌握实验箱电源、逻辑开关和 LED 电平指示的用法

- (7) 学习基本的数字电路的故障检查和排除方法

- ⑧ 学习 Mulitisim 逻辑化简操作和使用方法

#### 2、 时间要求:

实验时间:第6周、第7周

报告提交:第8周课内

### 3、 预备知识:

实验教材:

1.1 节、1.6 节、1.7 节、1.8 节、2.2 节、2.8 节、2.10 节、3.1 节、3.2 节、3.3 节 参考资料(中心网站提供下载):

"如何读懂数字逻辑器件数据手册" (pdf 文档)

"Multisim 软件使用手册" (pdf 文档)

"利用 Multisim 实现自动逻辑化简" (pdf 文档)

"Circuit Design Suite 12.0" (设计软件)

#### 4、 演示实验

演示 1.8 节内容

### 5、 必做实验:

- ① 数值判别电路

- a) 设计一个组合逻辑电路,它接收一位 8421BCD 码  $B_3B_2B_1B_0$ ,仅当  $2 < B_3B_2B_1B_0 < 7$  时输出 Y 才为 1 (第 6 周实验课内指导教师验收)

- b) 设计一个组合逻辑电路, 它接收 4 位 2 进制数 B<sub>3</sub>B<sub>2</sub>B<sub>1</sub>B<sub>0</sub>, 仅当 2 < B<sub>3</sub>B<sub>2</sub>B<sub>1</sub>B<sub>0</sub> < 7 时输出 Y 才为 1

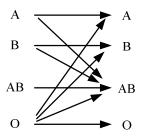

- ② 人类有四种血型: A、B、AB和O型。输血时,输血者与受血者必须符合下图的规定,否则有生命危险,利用数据选择器和最少数量的与非门,完成血型配对任务。(设计方案可参看数字逻辑电路实践教材 Page 86)

③ 设有三台用电设备 A、B、C 和两台发电机组 X、Y。X 机组功率为 10kW, Y 机组功率为 20kW。用电设备 A 用电量为 15kW,设备 B 用电量为 10kW,设备 C 用电量为 5kW,三台 用电设备有时同时工作,有时只有其中部分设备工作,甚至均不工作。试用 3-8 译码器设计一个供电控制电路控制发电机组,以达到节电的目的。(设计方案可参看数字逻辑电路实践教材 Page 83)

## 6、 选作实验

① 设计一个保险箱的数字密码锁,该锁有 4 位密码输入端( $A_0$ ,  $A_1$ ,  $A_2$ ,  $A_3$ )和一个开箱钥匙信号输入端(E)。当用钥匙开箱时(E=1),如果输入密码 = "1011",保险箱被打开( $Z_i$ =1);如果不符,电路将发生报警信号( $Z_2$ =1)。要求使用最少数量的与非门实现电路,检测并记录实验结果。

## 7、 预习项目

- ① 根据发的"课程准备事项要求",完成单股线的准备和面包板常用连接线的安装

- ② 完成所有必做实验的设计,并将设计方案、原理图、硬件连接示意图写在实验报告的原理 部分

- ③ 课前完成"数值判别电路"内容 a 电路搭接

## 实验二、可编程组合逻辑设计

## 1、 学习目标:

- ① 了解 TTL 和 CMOS 器件的静态特性和动态特性测量方法及这些特性对设计的影响

- ② 掌握通过数字器件手册查看器件静态和动态特性参数

- ③ 了解可编程数字系统设计的流程

- ④ 掌握 Quartus II 软件的使用方法

## 2、 时间要求:

实验时间:第8周、第9周

报告提交:第10周课内

## 3、 预备知识:

实验教材:

1.2 节、2.1 节、2.2 节、2.4 节、2.5 节、2.6 节、2.7 节、2.9 节、第 7 章 参考资料(中心网站提供下载):

"Quartus II 软件使用简介" (pdf 文档)

"Cyclone II 器件数据手册" (pdf 文档)

"Cyclone III 器件数据手册" (pdf 文档)

"Quartus II 9.0" (设计软件)

## 4、 演示实验

- ① 2.5 节内容 3 ,采用示波器 X-Y 方式测量并比较 74LS04 和 74HC04 两种器件的电压传输 特性  $V_0 = f(V_i)$

- ② 2.5 节内容 4, 用 74LS04 和 74HC04 门电路驱动能力

- ③ 2.5 节内容 5, 观察叠加交流噪声信号的影响(74LS04)

- ④ 2.7 节内容 1, 用环形振荡器测量 74LS04、74HC04 的传输延时时间

- ⑤ 2.7 节内容 2, 在 74LS04 传输延时测量电路中加入长导线, 观察延时造成的振荡周期变化

- ⑥ 介绍 Quartus II 软件使用

#### 5、 必做实验:

① 在 Quartus II 中用原理图输入方法,用一个 4 选 1 数据选择器实现如下逻辑函数:

$$Y(DCBA) = \sum m(0,1,2,5,8,10,12,13)$$

注:本实验内容在第8周课内验收

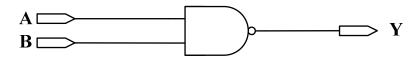

② 在 Quartus II 中用原理图输入方法,实现上图所示与非门,并利用 Quartus II 的软件仿真功

#### 能完成以下实验

- a) 输入 A 为 10ns 的时钟信号,输入 B = '1', 查看器件数据手册,在 I/O Bank1 中选择 3 个器件管脚分别分配给 A、B、Y。观察并记录功能仿真和时序仿真下 Y 的输出波形,并对结果进行分析

- b) 查看器件数据手册,在 I/O Bank1 中选择 2 个器件管脚分别分配给 A、B, I/O Bank2 中选择 1 个器件管脚分配给 Y, 重复 a 的实验内容中的时序仿真部分。

- e) 输入 A、B 都为 10ns 的时钟信号,但 B 比 A 延迟 5ns,查看器件数据手册,在 I/O Bank1 中选择 3 个器件管脚分别分配给 A、B、Y。观察并记录功能仿真和时序仿真下 Y 的输出波形,并对结果进行分析

- d) 查看器件数据手册,在 I/O Bank1 选择 1 个器件管脚分配给 A、I/O Bank3 选择 1 个器件管脚分配给 B, I/O Bank2 选择 1 个器件管脚分配给 Y。重复 c 实验内容中的时序仿真部分。

- ③ 下表是一个多向交通信号灯的信号切换表,切换顺序是从信号状态1逐一递增变换到信号状态7,然后再从状态7回到状态1,重复循环,试在FPGA中用中规模组合电路和门电路设计实现该功能,并下载到器件进行静态验证,验证时每个方向模式的信号用三个LED(分别标识红、绿、黄)显示。

| 信号状态 | 东西(左转) | 东西(直右) | 南北(左转) | 南北(直右) |

|------|--------|--------|--------|--------|

| 1    | 红      | 绿      | 红      | 红      |

| 2    | 红      | 黄      | 红      | 红      |

| 3    | 绿      | 红      | 红      | 红      |

| 4    | 黄      | 红      | 红      | 红      |

| 5    | 红      | 红      | 红      | 绿      |

| 6    | 红      | 红      | 红      | 黄      |

| 7    | 红      | 红      | 绿      | 红      |

| 8    | 红      | 红      | 黄      | 红      |

④ 用 FPGA 片内的 ROM 单元设计一个 8421BCD 码七段显示译码电路,其真值表如下表所示, 完成并测试其功能。

| $\mathbf{A}_3$ | $\mathbf{A}_2$ | $\mathbf{A}_1$ | $\mathbf{A}_{0}$ | dot | a | b | $\mathbf{c}$ | d | e | f | g | HEX |

|----------------|----------------|----------------|------------------|-----|---|---|--------------|---|---|---|---|-----|

| 0              | 0              | 0              | 0                | 0   | 0 | 0 | 0            | 0 | 0 | 0 | 1 | 01  |

| 0              | 0              | 0              | 1                | 0   | 1 | 0 | 0            | 1 | 1 | 1 | 1 | 4F  |

| 0              | 0              | 1              | 0                | 0   | 0 | 0 | 1            | 0 | 0 | 1 | 0 | 12  |

| 0              | 0              | 1              | 1                | 0   | 0 | 0 | 0            | 0 | 1 | 1 | 0 | 06  |

| 0              | 1              | 0              | 0                | 0   | 1 | 0 | 0            | 1 | 1 | 0 | 0 | 4C  |

| 0              | 1              | 0              | 1                | 0   | 0 | 1 | 0            | 0 | 1 | 0 | 0 | 24  |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 20 |

|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | OF |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 04 |

#### 6、 预习项目

- ① 所有必做实验的设计方案和原理图

- ② 参考"Quartus II 使用简介",在课前用 Quartus II 的原理图输入法完成必做内容 1 的原理图 绘制,并将设计文件拷贝带至实验室,上课前交由指导教师检查

## 实验三、时序逻辑电路

## 1、 学习目标:

- ① 掌握时序逻辑电路的一般设计过程

- ② 掌握时序逻辑电路的时延分析方法,了解时序电路对时钟信号相关参数的基本要求

- ③ 掌握时序逻辑电路的基本调试方法

- ④ 熟练使用示波器和逻辑分析仪观察波形图

## 2、 时间要求:

实验时间:第10周、第11周

报告提交:第12周

#### 3、 预备知识:

实验教材: 第4章

#### 4、 必做实验:

① 广告流水灯(第10周课内验收)

用触发器、组合函数器件和门电路设计一个广告流水灯,该流水灯由8个LED组成,工作时始终为1暗7亮,且这一个暗灯循环右移。

- (1) 写出设计过程, 画出设计的逻辑电路图, 按图搭接电路

- (2) 将单脉冲加到系统时钟端,静态验证实验电路

- (3) 将 TTL 连续脉冲信号加到系统时钟端, 用示波器观察并记录时钟脉冲 CP、触发器的输出端 Q2、Q1、Q0 和 8 个 LED 上的波形。

#### ② 序列发生器

用 MSI 计数器和移位寄存器设计一个具有自启动功能的 01011 序列信号发生器,

- (1) 写出设计过程, 画出电路逻辑图

- (2) 搭接电路,并用单脉冲静态验证实验结果

- (3) 加入 TTL 连续脉冲,用示波器观察观察并记录时钟脉冲 CLK、序列输出端的波形。

- ③ 多方向交通灯(第11周课内验收,基础要求占本次实验分的80%,扩展要求占20%)

设计一个多方向交通灯,包括左转、直行和右转信号,时间用数码管显示,信号用 LED 显示,信号切换时间表如下表所示其中信号切换时间表 A 为基础要求,信号切换时间表 B 为扩展要求

- (1) 写出设计过程, 画出电路逻辑图

- (2) 搭接电路(可修改利用实验二中已经完成的组合单元),验证实验结果

#### 信号切换时间表 A

| 时间(s) | 东西(左转) | 东西(直右) | 南北(左转) | 南北(直右) |

|-------|--------|--------|--------|--------|

| 40    | 红      | 绿      | 红      | 红      |

| 40    | 绿      | 红      | 红      | 红      |

| 40    | 红      | 红      | 红      | 绿      |

| 40    | 红      | 红      | 绿      | 红      |

#### 信号切换时间表 B

| 时间(s) | 东西(左转) | 东西(直右) | 南北(左转) | 南北(直右) |

|-------|--------|--------|--------|--------|

| 40    | 红      | 绿      | 红      | 红      |

| 4     | 红      | 黄      | 红      | 红      |

| 40    | 绿      | 红      | 红      | 红      |

| 4     | 黄      | 红      | 红      | 红      |

| 40    | 红      | 红      | 红      | 绿      |

| 4     | 红      | 红      | 红      | 黄      |

| 40    | 红      | 红      | 绿      | 红      |

| 4     | 红      | 红      | 黄      | 红      |

### 5、 预习项目

- ① 广告流水灯和序列发生器的设计方案、原理图、硬件连接图(第10周)

- ② 广告流水灯电路搭接(第10周)

- ③ 多方向交通灯的设计方案、原理图、硬件连接图(第11周)

- ④ 多方向交通灯电路搭接(第11周)

## 实验四、FPGA时序逻辑设计

#### 1、学习目标

- ① 了解可编程数字系统设计的流程

- ② 掌握 Quartus II 软件的使用方法

③ 掌握原理图输入方式设计时序逻辑电路的方法和流程

#### 2、 时间要求:

实验时间:第12周、第13周

报告提交:第14周

3、 预备知识:

实验教材:第4章、第7章

4、 必做实验:

按学号尾数指定要完成的实验项目, 所有实验项目将在第10周周末在实验中心网站发布

- 5、 预习检目

- ① 系统设计过程、顶层模块框图、单元模块框图、模块电路原理图

- ② 第12周,根据指导教师指定的时间和地点,检查预习报告

## 实验五、FPGA 系统设计

## 1、 学习目标

- ① 综合前面所学的各项内容

- ② 了解可编程数字系统设计的流程

- ③ 掌握 Quartus II 软件的使用方法

- ④ 掌握原理图输入方式设计数字系统的方法和流程

#### 2、 时间要求:

实验时间:第14周、第15周

报告提交:第16周

3、 预备知识:

实验教材: 第6章、第7章

4、 必做实验:

按学号尾数指定要完成的实验项目,所有实验项目将在第12周周末在实验中心网站发布

- 5、 预习检目

- ① 系统设计过程、顶层模块框图、单元模块框图、模块电路原理图

- ② 第 14 周,根据指导教师指定的时间和地点,检查预习报告